随着微电子工业的发展,集成电路的尺寸不断缩小、布线密度不断增加,随之产生的阻容延迟、串扰噪声和能量损耗已成为制约其发展的关键瓶颈问题,这对集成电路内互连隔离电介质材料的介电常数(k)提出了更高的要求。国际元件及系统技术蓝图指出,在2028年之前亟需发展k值小于2的超低介电常数材料。现有的低k材料,如二氧化硅衍生物、有机高分子材料以及多孔材料等通常k值大于2且存在热稳定性、机械性能较差等问题,难以满足实际加工中的工艺要求。

多面体寡聚倍半硅氧烷(POSS)因其优异的热稳定性、力学性能以及独特的笼状结构,被认为是制备低介电常数的理想构筑单元或填料。然而,以往基于POSS的低k材料均围绕T8 POSS展开,尚未有研究探索笼子尺寸更大的T10和T12 POSS在低k材料制备上的潜力(理论上增大POSS的笼子尺寸能引入更多的孔隙,进一步降低材料的k值)。这主要是因为T8 POSS通常易合成且存在商业化产品,而T10和T12 POSS的制备及纯化仍然存在着较大难度。

图1 c-T8B8、c-T10B10和c-T12B12的制备路线图

在本研究中,他们首先以商业化的乙烯基POSS混合物为原料,采用柱层析法,利用八乙烯基POSS(T8V8)、十乙烯基POSS(T10V10)和十二乙烯基POSS(T12V12)的极性差异依次实现了分离;随后通过硅氢加成反应在其外围修饰上了苯并环丁烯基团,经热交联制备出了三种有机-无机杂化材料(c-T8B8、c-T10B10和c-T12B12),制备路线如图1所示。

图2 c-T8B8、c-T10B10和c-T12B12三种材料相应的POSS笼体积和介电常数之间的关系以及基于更大尺寸的T14、T16和T18 POSS的材料的介电常数预测值

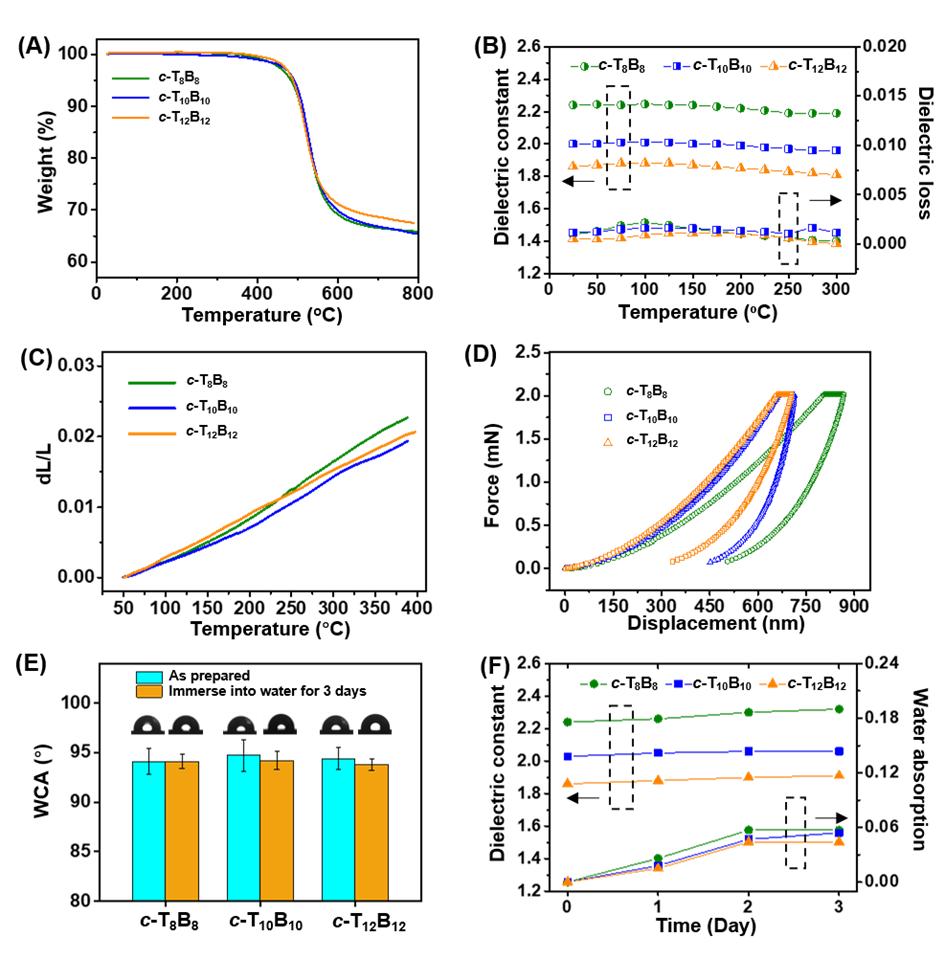

研究发现随着POSS笼子尺寸的增加,材料的k值和损耗都呈现下降趋势(c-T8B8、c-T10B10和c-T12B12在1 MHz时的k值分别2.24、2.02和1.83,损耗分别为0.003,0.0018和0.0015)。正电子湮灭寿命谱证明增大POSS笼子尺寸能赋予材料更多的孔隙(图3),这也是k值降低的主要原因。有趣的是,该体系中材料的k值与相应POSS的体积呈现线性关系(如图2所示)。可以预见的是,使用更大笼子尺寸的T14、T16和T18 POSS有望将材料的k值降低到1.5以下。此外,所得材料还呈现出优异的综合性能,如高透明性、低表面粗糙度(图4)、优异的热稳定性和力学性能、疏水性,即使在水中浸泡3天或在300℃高温下,这些材料依然能维持优异的介电性能(图5)。本项工作不仅为综合性能优异的超低介电常数材料的开发提供了新的思路,也为未来集成电路用超低介电常数材料提供了备选。

图3 c-T8B8、c-T10B10和c-T12B12三种材料的正电子湮灭寿命谱

图4 c-T8B8、c-T10B10和c-T12B12三种材料的透明性和表面粗糙度

图5 c-T8B8、c-T10B10和c-T12B12三种材料的 (A) 热失重曲线,(B)25-300℃的介电常数和损耗,(C) 温度-形变曲线,(D) 纳米压痕曲线,(E) 水接触角,(E) 在水中浸泡3天后的介电常数和损耗

原文链接:https://onlinelibrary.wiley.com/doi/full/10.1002/adfm.202102074

全文链接:http://www.polymer.cn/sci/kjxw18274.html